Marvell delivers advanced packaging platform for custom AI accelerators

Novel multi-die packaging platform enables multi-die architectures with lower power consumption and reduced total cost.

Marvell Technology has expanded the packaging ecosystem for AI infrastructure with an innovative multi-die solution that lowers total cost of ownership (TCO) for custom AI accelerator silicon. The advanced packaging platform is part of the Marvell™ comprehensive IP portfolio for custom AI compute platforms—and enables multi-chip accelerator designs 2.8x larger than conventional single-die implementations. The Marvell approach can enable more efficient die-to-die interconnect, lower power consumption, increased chiplet yields and lower product cost, and provides a manufacturing alternative to traditional interposer-based multi-chip approaches. The packaging platform has been qualified with a major hyperscaler and is now ramping in production.

In the AI era, chip packaging has become critical for increasing compute density while effectively managing power, thermal dissipation, optical I/O, signal integrity, and other factors that impact the performance and reliability in multi-die chiplet designs. Simultaneously, rising supply chain complexity and extended lead times present significant challenges for scaling advanced packaging solutions. The new Marvell packaging solution enables hyperscalers to overcome these barriers, accelerating time-to-market while offering supply chain flexibility.

This is the latest innovation in a series of advancements for customers of Marvell custom XPU solutions. This highly optimized multi-chip packaging platform was designed from the ground up with the recently announced Marvell custom HBM and CPO solutions in mind. Taken together, Marvell is building the industry's broadest technology platform to enable custom XPU design for the future.

"Advanced packaging is one of the primary vehicles for advancing compute density in AI clusters and cloud," said Will Chu, senior vice president and general manager of Custom Cloud Solutions at Marvell. "Without it, AI infrastructure would be significantly more expensive and power-hungry. We look forward to collaborating with our partners and customers to further unlock the potential of advanced packaging."

"Chiplets constitute one of the most dynamic segments of the semiconductor market. We anticipate that chiplet processor revenue will grow by 31% per year to reach $145 billion by 2030," said James Sanders, senior analyst at TechInsights. "Advanced packaging technologies are critical to the evolution of chiplets, giving designers a framework in which to experiment."

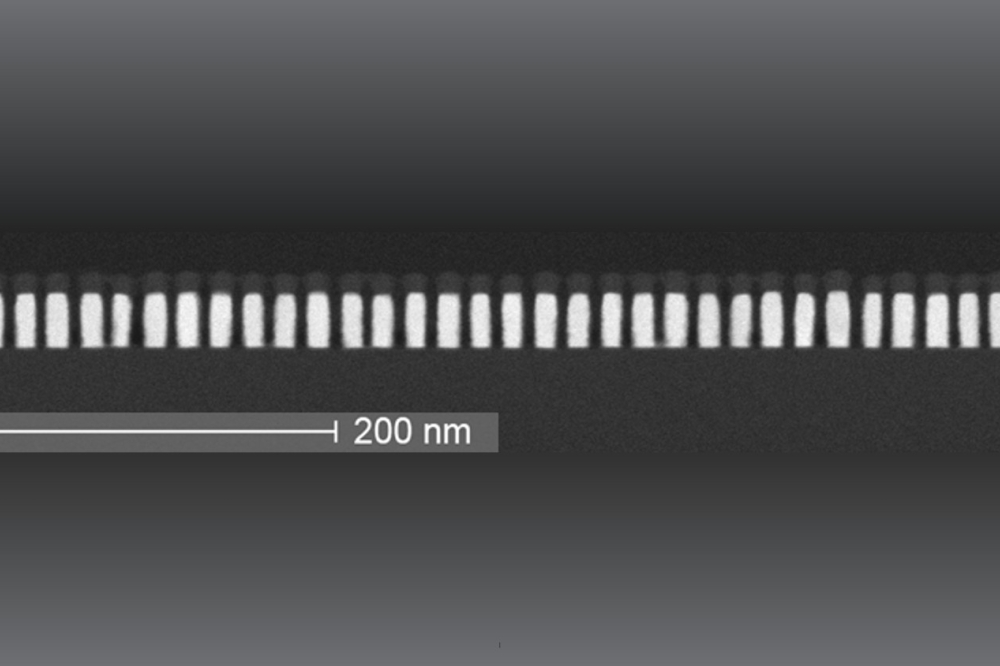

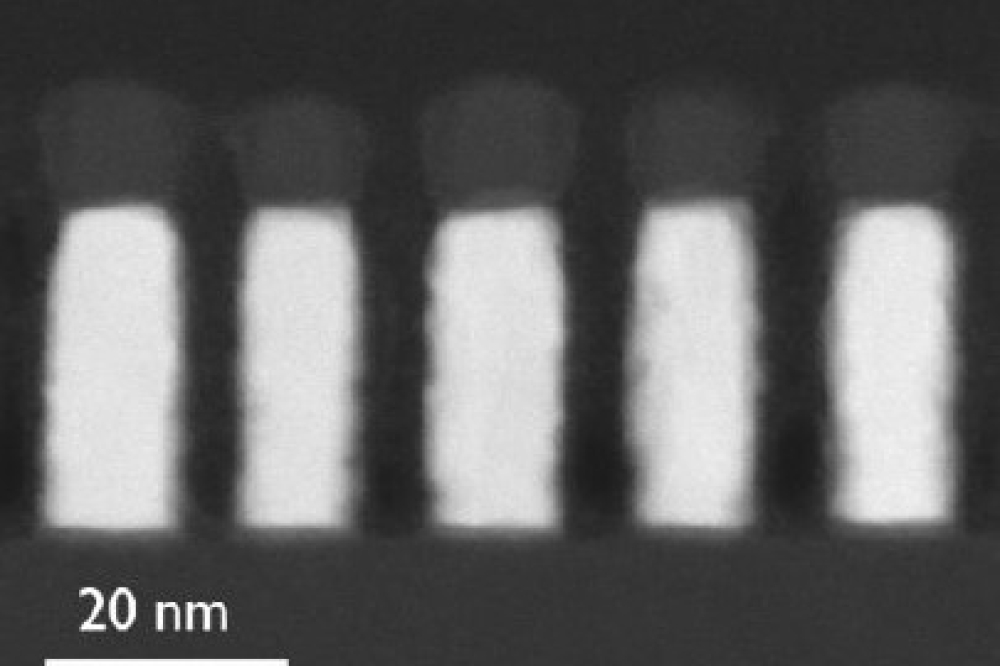

Interposers serve as the foundational layer with compute, dies, memory, and other components stacked above and communicating through the interposer. The Marvell re-distribution layer (RDL) offers a compelling alternative to traditional silicon interposers for data center applications. The Marvell approach integrates 1390 mm2 of silicon and four pieces of high-bandwidth memory 3/3E (HBM3/3E) memory stacks and utilizes six interposer RDL layers. This enables multi-die AI accelerator solutions that are 2.8 times larger than the largest possible single-chip design. The Marvell multi-die packaging solution allows for shorter die-to-die interconnects and a modular RDL interposer.

The Marvell RDL interposer reduces design cost through its modular design. In conventional chiplets, a single interposer will span the floor space of the chips it connects well as any area between them. If two computing cores are on opposite sides of a chiplet package, the interposer will cover the entire space. By contrast, Marvell RDL interposers are form-fitted to individual computing dies and connected by high-bandwidth paths. Not only does this approach reduce materials, it also increases chiplet yields by enabling manufacturers to replace individual dies.

The Marvell multi-die packaging platform enables the integration of passive devices to reduce potential signal noise within the chiplet package caused by the power supply. In collaboration with the packaging ecosystem, Marvell has extended the solution to support multiple components within a single package, enabling the integration of the most complex AI designs.

In addition, hyperscalers can now employ the packaging technology to build XPUs with HBM3 and HBM3E memory and Marvell is actively qualifying the technology for future HBM4 designs.